Процессор / Хабр

Сколько я себя помню, всегда мечтала сделать процессор. Наконец, вчера я его сделала. Не бог весть что: 8 бит, RISC, текущая рабочая частота — 4 кГц, но он работает. Пока что в программе моделирования логических цепей, но все мы знаем: «сегодня — на модели, завтра — на деле!».

Под катом несколько анимаций, краткое введение в двоичную логику для самых маленьких, короткий рассказ про основные микросхемы логики процессора и, собственно, схема.

Двоичная логика

Двоичная система счисления (для тех, кто не в курсе) — это такая система счисления, в которой нет цифр больше единицы. Такое определение многих сбивает с толку, пока они не вспомнят, что в десятичной системе счисления нет цифр больше девятки.

Двоичная система используется в компьютерах потому, что числа в ней легко кодировать напряжением: есть напряжение — значит, единица; нет напряжения — значит, ноль. Кроме того, «ноль» и «один» легко можно понимать как «ложно» и «истинно». Более того, большая часть устройств, работающих в двоичной системе счисления, обычно относится к числам как к массиву «истинностей» и «ложностей», то есть оперирует с числами как с логическими величинами. Для самых маленьких и тех, кто не в курсе, я расскажу и покажу, как работают простейшие элементы двоичной логики.

Более того, большая часть устройств, работающих в двоичной системе счисления, обычно относится к числам как к массиву «истинностей» и «ложностей», то есть оперирует с числами как с логическими величинами. Для самых маленьких и тех, кто не в курсе, я расскажу и покажу, как работают простейшие элементы двоичной логики.

Элемент «Буфер»

Представьте, что вы сидите в своей комнате, а ваш друг — на кухне. Вы кричите ему: «Друг, скажи, в коридоре горит свет?». Друг отвечает: «Да, горит!» или «Нет, не горит». Ваш друг — буфер между источником сигнала (лампочкой в коридоре) и приемником (вами). Более того, ваш друг — не какой-нибудь там обычный буфер, а буфер управляемый. Он был бы обычным буфером, если бы постоянно кричал: «Лампочка светится» или «Лампочка не светится».

Элемент «Не» — NOT

А теперь представьте, что ваш друг — шутник, который всегда говорит неправду. И если лампочка в коридоре светится, то он скажет вам «Нет, в коридоре совсем-совсем темно», а если не светится — то «Да, в коридоре свет горит». Если у вас есть такой друг на самом деле, значит, он воплощение элемента «Не».

Если у вас есть такой друг на самом деле, значит, он воплощение элемента «Не».

Элемент «Или» — OR

Для объяснения сути элемента «Или» одной лампочки и одного друга, к сожалению, не хватит. Нужно две лампочки. Итак, у вас в коридоре две лампочки — торшер, к примеру, и люстра. Вы кричите: «Друг, скажи, хотя бы одна лампочка в коридоре светит?», и ваш друг отвечает «Да» или «Нет». Очевидно, что для ответа «Нет» все лампочки обязательно должны быть выключены.

Элемент «И» — AND

Та же самая квартира, вы, друг на кухне, торшер и люстра в коридоре. На ваш вопрос «В коридоре обе лампочки горят?» вы получаете ответ «Да» или «Нет». Поздравляю, теперь ваш друг — это элемент «И».

Элемент «Исключающее Или» — XOR

Повторим еще раз эксперимент для элемента «Или», но переформулируем свой вопрос к другу: «Друг, скажи, в коридоре только одна лампочка светит?». Честный друг ответит на такой вопрос «Да» только в том случае, если в коридоре действительно горит только одна лампочка.

Сумматоры

Четвертьсумматор

Четвертьсумматором называют элемент «Исключающее Или». Почему? Давайте разберемся.

Составим таблицу сложения для двух чисел в двоичной системе счисления:

0+0= 0

0+1= 1

1+0= 1

1+1= 10

Теперь запишем таблицу истинности элемента «Исключающее Или». Для этого обозначим светящуюся лампочку за 1, потухшую — за 0, и ответы друга «Да»/«Нет» как 1 и 0 соответственно.

0 XOR 1 = 1

1 XOR 0 = 1

1 XOR 1 = 0

Очень похоже, не так ли? Таблица сложения и таблица истинности «Исключающего Или» совпадают полностью, кроме одного-единственного случая. И этот случай называется «Переполнение».

Полусумматор

При переполнении результат сложения уже не помещается в столько же разрядов, во сколько помещались слагаемые. Слагаемые — два однозначных числа (одна значащая цифра, понимаете?), а сумма — уже двузначное (две значащих цифры). Две цифры одной лампочкой («Светится»/«Не светится») уже не передать.

Кроме XOR, для сумматора нам потребуется элемент «И» (AND).

0 XOR 0 = 0 0 AND 0 = 0

0 XOR 1 = 1 0 AND 1 = 0

1 XOR 0 = 1 1 AND 0 = 0

1 XOR 1 = 0 1 AND 1 = 1

Тадам!

0+0= 00

0+1= 01

1+0= 01

1+1= 10

Наша вундервафля полусумматор работает. Его можно считать простейшим специализированным процессором, который складывает два числа. Полусумматор называется полусумматором потому, что с его помощью нельзя учитывать перенос (результат работы другого сумматора), то есть нельзя складывать три однозначных двоичных числа. В связи с этим из нескольких одноразрядных полусумматоров нельзя сделать один многоразрядный.

Я не буду вдаваться в подробности работы полных и многоразрядных сумматоров, просто надеюсь, что основную идею вы уловили.

Более сложные элементы

Мультиплексор

Предлагаю снова включить воображение. Итак, представьте. Вы живете в частном одноквартирном доме, возле двери этого дома стоит ваш почтовый ящик. Выходя на прогулку, вы замечаете странного почтальона, который стоит возле этого самого почтового ящика. И вот что он делает: достает кучу писем из сумки, читает номер на почтовом ящике, и в зависимости от номера на ящике бросает в него то или иное письмо. Почтальон работает мультиплексором. Он определенным образом (номер на конверте) определяет, какой отправить сигнал (письмо) по сигнальной линии (почтовый ящик).

Вы живете в частном одноквартирном доме, возле двери этого дома стоит ваш почтовый ящик. Выходя на прогулку, вы замечаете странного почтальона, который стоит возле этого самого почтового ящика. И вот что он делает: достает кучу писем из сумки, читает номер на почтовом ящике, и в зависимости от номера на ящике бросает в него то или иное письмо. Почтальон работает мультиплексором. Он определенным образом (номер на конверте) определяет, какой отправить сигнал (письмо) по сигнальной линии (почтовый ящик).

Мультплексоры состоят обычно только из сочетаний элементов «И», «Или» и «Не». У одноразрядного мультиплексора один вход называется «выбор адреса», два входа с общим названием «входной сигнал» и один выход, который так и называется: «выходной сигнал».

Когда на «выбор адреса» подается 0, то «выходной сигнал» становится таким же, как первый «входной сигнал». Соответственно, когда на «выбор» подается 1, то «выходной сигнал» становится равным второму «входному сигналу».

Демультиплексор

А вот эта штучка работает с точностью до наоборот.

Счетчик

Для понимания работы счетчика вам опять понадобится ваш друг. Позовите его из кухни (надеюсь, он не сильно там скучал, и, главное, не съел всю вашу еду), и попросите делать вот что: пусть он запомнит число 0. Каждый раз, когда вы будете прикасаться к нему, он должен прибавить единицу к тому числу, которое помнит, сказать результат и запомнить его. Когда результат будет равен (допустим) 3, он должен выкрикнуть «Абракадабра!» и отвечать при следующем прикосновении, что сейчас он помнит число 0. Немного сложно? Смотрите:

Вы прикасаетесь к другу. Друг говорит «Один».

Вы прикасаетесь к другу. Друг говорит «Два».

Вы прикасаетесь к другу. Друг говорит «Три». Друг выкрикивает «Хабрахабр!». Критическая атака! Вы временно парализованы и не можете двигаться.

Вы прикасаетесь к другу. Друг говорит «Ноль».

Ну, и так далее. Очень просто, верно?

Очень просто, верно?

Вы, конечно, поняли, что ваш друг сейчас — это счетчик. Прикосновение к другу можно считать «тактирующим сигналом» или, попросту говоря, сигналом продолжения счета. Крик «Абракадабра» показывает, что запомненное значение в счетчике — максимальное, и что при следующем тактирующем сигнале счетчик будет установлен в ноль. Есть два отличия двоичного счетчика от вашего друга. Первое: настоящий двоичный счетчик выдает запомненное значение в двоичном виде. Второе: он всегда делает только то, что вы ему говорите, и никогда не опускается до дурацких шуточек, способных нарушить работу всей процессорной системы.

Память

Триггер

Давайте продолжим издеваться над вашим несчастным (возможно, даже воображаемым) другом. Пусть теперь он запомнит число ноль. Когда вы касаетесь его левой руки, он должен запоминать число ноль, а когда правой — число один. При вопросе «Какое число ты помнишь?» друг должен всегда отвечать то число, которое запоминал — ноль или один.

Простейшей запоминающей ячейкой является RS-триггер («триггер» значит «переключатель»). RS-триггер может хранить в себе один бит данных («ноль»/«один»), и имеет два входа. Вход Set/Установка (совсем как левая рука вашего друга) записывает в триггер «один», а вход Reset/Сброс (соответственно, правая рука) — «ноль».

Регистр

Немного сложнее устроен регистр. Ваш друг превращается в регистр тогда, когда вы просите его что-нибудь запомнить, а потом говорите «Эй, напомни мне, что я говорил тебе запомнить?», и друг правильно отвечает.

Регистр обычно может хранить в себе чуть больше, чем один бит. У него обязательно есть вход данных, выход данных и вход разрешения записи. С выхода данных вы в любой момент можете прочитать то, что в этом регистре записано. На вход данных вы можете подавать те данные, которые хотите в этот регистр записать. Можете подавать данные до тех пор, пока не надоест. В регистр все равно ничего не запишется до тех пор, пока на вход разрешения записи не подать один, то есть «логическую единицу».

Сдвиговый регистр

Вы когда-нибудь стояли в очередях? Наверняка стояли. Значит, вы представляете, каково быть данными в сдвиговом регистре. Люди приходят и становятся в конец очереди. Первый человек в очереди заходит в кабинет к большой шишке. Тот, кто был вторым в очереди, становится первым, а тот, кто был третьим — теперь второй, и так далее. Очередь — это такой хитрый сдвиговый регистр, из которого «данные» (ну, то есть люди) могут убегать по делам, предварительно предупредив соседей по очереди. В настоящем сдвиговом регистре, разумеется, «данные» из очереди сбегать не могут.

Итак, у сдвигового регистра есть вход данных (через него данные попадают в «очередь») и выход данных (из которого можно прочитать самую первую запись в «очереди»). Еще у сдвигового регистра есть вход «сдвинуть регистр». Как только на этот вход приходит «логическая единица», вся очередь сдвигается.

Есть одно важное различие между очередью и сдвиговым регистром. Если сдвиговый регистр расчитан на четыре записи (например, на четыре байта), то первая в очереди запись дойдет до выхода из регистра только после четырех сигналов на вход «сдвинуть регистр».

Оперативная память

Если много-много триггеров объединить в регистры, а много-много регистров объединить в одной микросхеме, то получится микросхема оперативной памяти. У микросхемы памяти обычно есть вход адреса, двунаправленный вход данных (то есть в этот вход можно записывать, и с него же можно считывать) и вход разрешения записи. На вход адреса подаем какое-нибудь число, и это число выберет определенную ячейку памяти. После этого на входе/выходе данных мы можем прочитать то, что записано в эту самую ячейку.

Теперь мы одновременно подадим на вход/выход данных то, что хотим в эту ячейку записать, а на вход разрешения записи — «логическую единицу». Результат немного предсказуем, не так ли?

Процессор

BitBitJump

Процессоры иногда делят на CISC — те, которые умеют выполнять много разных команд, и RISC — те, которые умеют выполнять мало команд, но выполняют их хорошо. Одним прекрасным вечером мне подумалось: а было бы здорово, если бы можно было сделать полноценный процессор, который умеет выполнять всего одну команду. Вскоре я узнала, что существует целый класс однокомандных процессоров — OISC, чаще всего они используют команду Subleq (вычесть, и если меньше или равно нулю, то перейти) или Subeq (вычесть, и если равно нулю, то перейти). Изучая различные варианты OISC-процессоров, я нашла в сети сайт Олега Мазонки, который разработал простейший однокомандный язык BitBitJump. Единственная команда этого языка так и называется — BitBitJump (скопировать бит и перейти по адресу). Этот, безусловно эзотерический, язык является полным по Тьюрингу — то есть на нем можно реализовать любой компьютерный алгоритм.

Вскоре я узнала, что существует целый класс однокомандных процессоров — OISC, чаще всего они используют команду Subleq (вычесть, и если меньше или равно нулю, то перейти) или Subeq (вычесть, и если равно нулю, то перейти). Изучая различные варианты OISC-процессоров, я нашла в сети сайт Олега Мазонки, который разработал простейший однокомандный язык BitBitJump. Единственная команда этого языка так и называется — BitBitJump (скопировать бит и перейти по адресу). Этот, безусловно эзотерический, язык является полным по Тьюрингу — то есть на нем можно реализовать любой компьютерный алгоритм.

Подробное описание BitBitJump и ассемблер для этого языка можно найти на сайте разработчика. Для описания алгоритма работы процессора достаточно знать следующее:

1. При включении процессора в регистрах PC, A и B записаны 0

2. Считываем ячейку памяти с адресом PC и сохраняем прочитанное в регистр A

3. Увеличиваем PC

4. Считываем ячейку памяти с адресом PC и сохраняем прочитанное в регистр B

5. Увеличиваем PC

Увеличиваем PC

6. Записываем в ячейку с адресом, записанным в регистре B, содержимое бита с адресом А.

7. Считываем ячейку памяти с адресом PC и сохраняем прочитанное в регистр B

8. Записываем в регистр PC содержимое регистра B

9. Переходим к пункту 2 нашего плана10. PROFIT!!!

К сожалению, алгоритм бесконечный, и потому PROFIT достигнут не будет.

Собственно, схема

Схема строилась стихийно, поэтому правят бал в ней страх, ужас и кавардак. Тем не менее, она работает, и работает прилично. Чтобы включить процессор, нужно:

1. Ввести программу в ОЗУ

2. Нажать на включатель

3. Установить счетчик в положение 4 (это можно делать и аппаратно, но схема стала бы еще более громоздкой)

4. Включить тактовый генератор

Как видите, использованы один регистр, один сдвиговый регистр, одна микросхема ОЗУ, два двоичных счетчика, один демультиплексор (представленный компараторами), два мультиплексора и немного чистой логики.

Можете скачать схему в формате circ для программы Logisim, и поиграться.

Что дальше?

Во-первых, можно увеличить разрядность процессора — заменив 8-битные элементы на 16-битные.

Во-вторых, можно вынести ОЗУ из процессора, и добавить несложную схему, которая будет приостанавливать процессор, изменять ОЗУ и снова включать процессор. Такая схема будет выполнять функции простого контроллера ввода-вывода. Тогда можно будет сделать на базе этого процессора калькулятор, контроллер или еще какую-нибудь забавную бесполезную штуку.

В-третьих, можно воплотить всю эту схему в железе. Что я собираюсь сделать. Как только сделаю — обязательно расскажу и покажу.

Спасибо всем за внимание!

P.S. Ссылки (для тех, кому лень читать):

1. Процессоры URISC — ru.wikipedia.org/wiki/Urisc

2. Сайт языка BitBitJump — mazonka.com/bbj/index.html

3. Программа для моделирования логических схем Logisim — http://ozark.hendrix.edu/~burch/logisim/

4. Самодельный URISC (ORISC) процессор для Logisim — narod.ru/disk/31367690001/oo.circ.html

Самодельный URISC (ORISC) процессор для Logisim — narod.ru/disk/31367690001/oo.circ.html

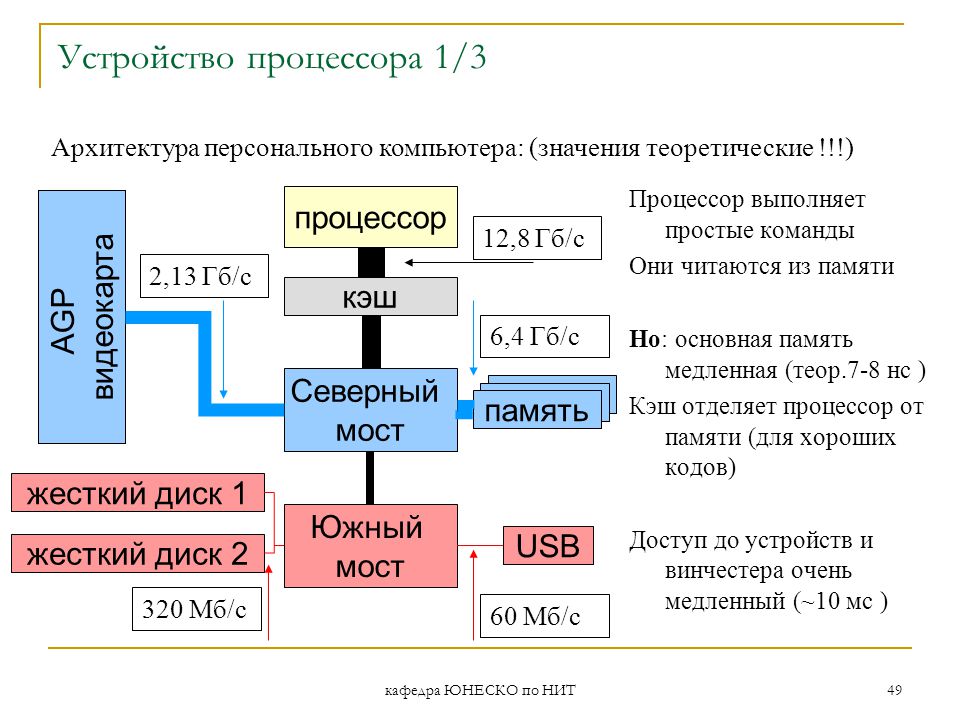

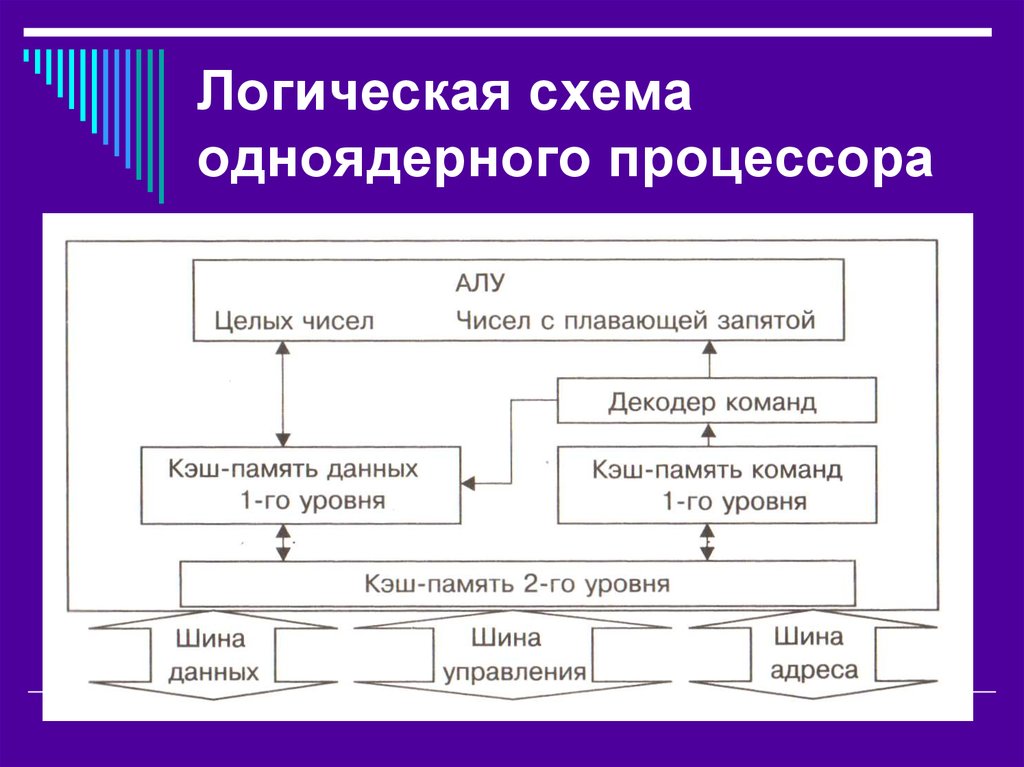

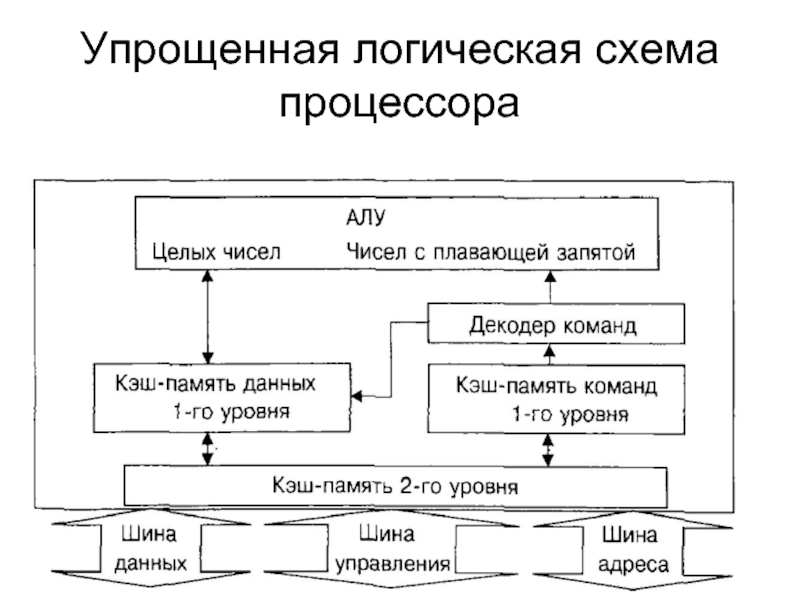

Упрощенная логическая схема одноядерного процессора

1. Процессор

УПРОЩЕННАЯ ЛОГИЧЕСКАЯ СХЕМА ОДНОЯДЕРНОГО ПРОЦЕССОРААрифметико-логическое устройство

Целых чисел

Чисел с плавающей запятой

Декодер команд

Кэш-память данных

1-го уровня

Кэш-память команд

1-го уровня

Кэш-память 2-го уровня

Шина

данных

Шина

управления

Шина

адреса

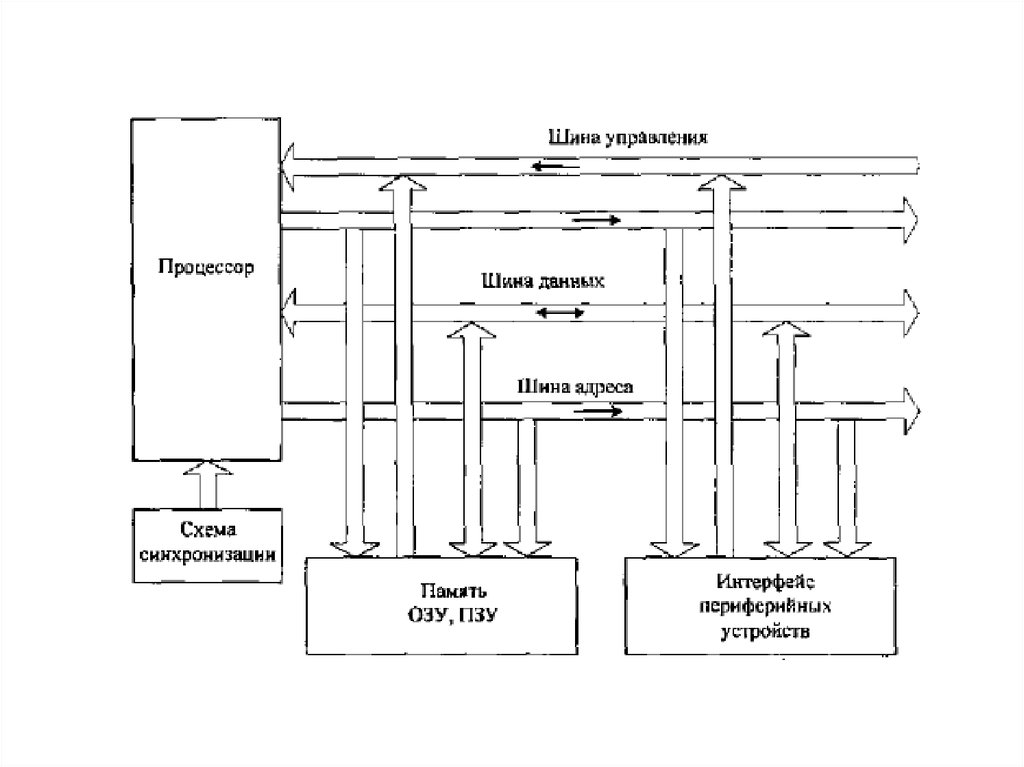

Оперативная память

Процессор

Шина данных (8, 16, 32, 64 бита)

Информационная магистраль (шина)

Шина адреса (16, 20, 24, 32, 36, 64 бита)

Шина управления

ТЕХНОЛОГИЯ ИЗГОТОВЛЕНИЯ ПРОЦЕССОРА

Восемь слоев кристалла процессора в 65нанометровом технологическом процессе

ПРОЦЕССОРЫ

Размер элемента:

10 мк = 10-5 м

Количество элементов:

2300

Самый первый процессор

Intel 4004 (1971 год)

Размер элемента:

65 нм = 0,065 мк = 10-8 м

Количество элементов:

291 000 000

Современный процессор

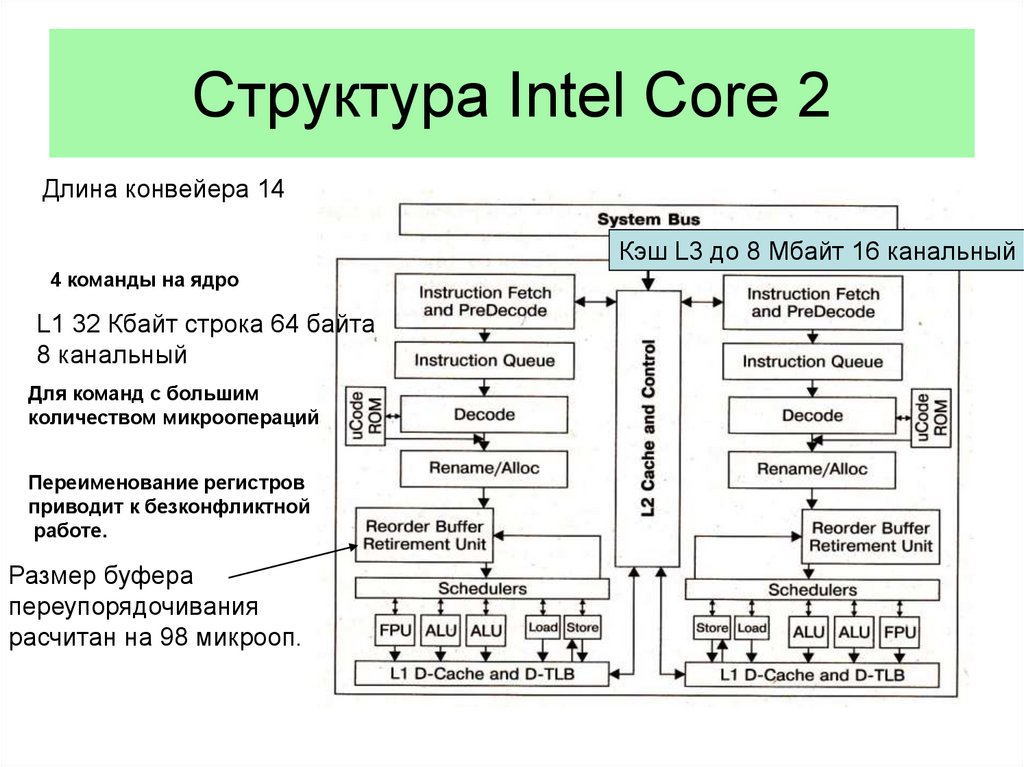

Intel Core 2 Duo (2007 год)

Ядро процессора Intel Core 2 Duo

ПРОИЗВОДИТЕЛЬНОСТЬ ПРОЦЕССОРА

Производительность процессора характеризует скорость выполнения приложений.

Производительность ~ Разрядность × Частота × Кол-во команд за такт

Разрядность процессора определяется количеством

двоичных разрядов, которые процессор обрабатывает за один

такт.

С момента появления первого процессора 4004 разрядность

процессора увеличилась в 16 раз ( с 4 бит до 64 битов).

Частота соответствует количеству тактов обработки данных,

которые процессор производит за 1 секунду.

С момента появления первого процессора частота

процессора увеличилась в 37 000 раз ( с 0,1 МГц до 3700 МГц).

Выделение процессором теплоты Q пропорционально

потребляемой мощности P, которая, в свою очередь

пропорциональна квадрату частоты ν2: Q ~ P ~ ν2

Для отвода тепла от процессора применяют массивные

воздушные системы охлаждения (кулеры).

Кулер для процессора

ПРОИЗВОДИТЕЛЬНОСТЬ ПРОЦЕССОРА

В настоящее время

производительность

процессора увеличивается

путем совершенствования

архитектуры процессора.

Во-первых, в структуру

процессора вводится кэшпамять 1-го и 2-го уровней,

которая позволяет ускорить

выборку команд и данных и тем

самым уменьшить время

выполнения одной команды.

Во-вторых, вместо одного

ядра процессора используется

два ядра, что позволяет

повысить производительность

процессора примерно на 80%.

КОМПЬЮТЕРНЫЙ ПРАКТИКУМ

1. Определение объемов кэш-памяти процессора

Кэш-память данных 1-го уровня –

16 Кбайт

Кэш-память команд 1-го уровня –

12 Кбайт

Кэш-память 2-го уровня –

1024 Кбайт

КОМПЬЮТЕРНЫЙ ПРАКТИКУМ

2. Определение температуры процессора

Количество оборотов в

минуту кулера процессора –

2884 об/мин

Температура процессора –

46 °С

КОМПЬЮТЕРНЫЙ ПРАКТИКУМ

3. Производительность процессора

КОМПЬЮТЕРНЫЙ ПРАКТИКУМ

3. Производительность процессора

Количество целочисленных операций:

6565 MIPS

.

КОМПЬЮТЕРНЫЙ ПРАКТИКУМ

3.

Производительность процессора

Производительность процессораКоличество операций с плавающей точкой :

8440 MFLOPS

.

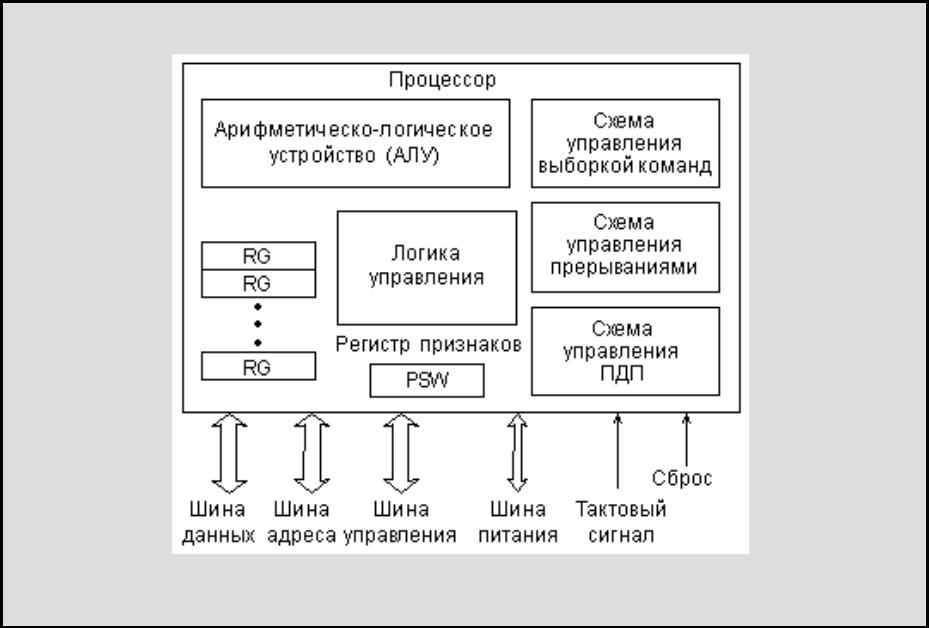

03. Назначение и структура процессора. Назначение и взаимодействие основных блоков. Классификация процессоров.

Назначение. Принцип работы.

Процессором — называется устройство, непосредственно осуществляющее процесс обработки данных и программное управление этим процессом. Процессор дешифрует и выполняет команды программ, организует обращение к ОП, инициирует работу ПУ, воспринимает и обрабатывает внешние события.

Процессор осуществляет управление взаимодействием всех устройств ЭВМ. (при наличии специальных процессоров эти функции рассредотачиваются).

Общая функциональная структура МП.

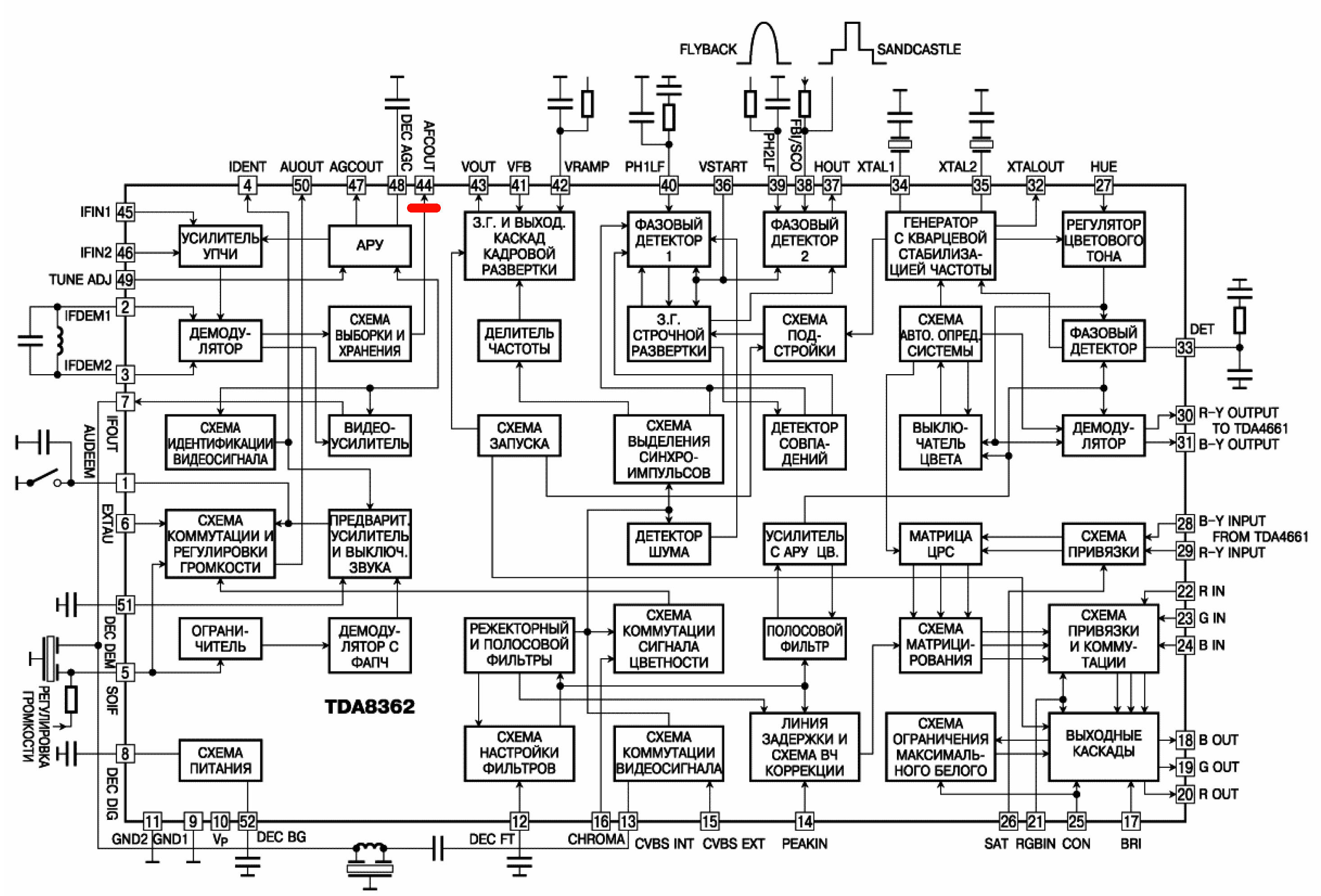

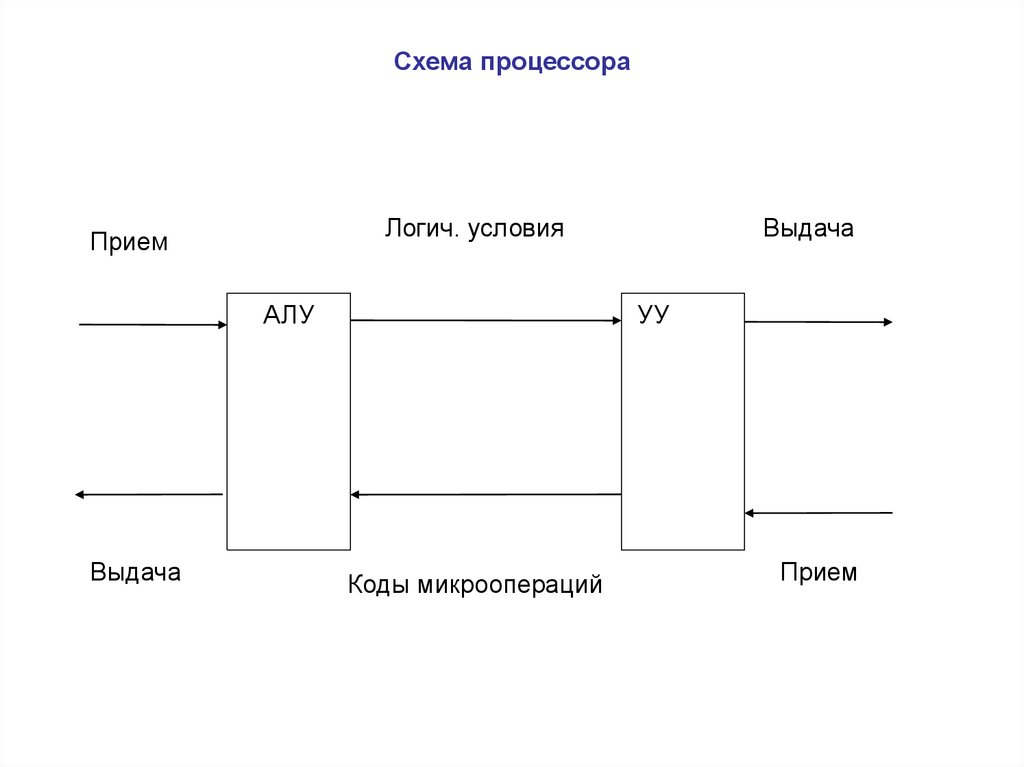

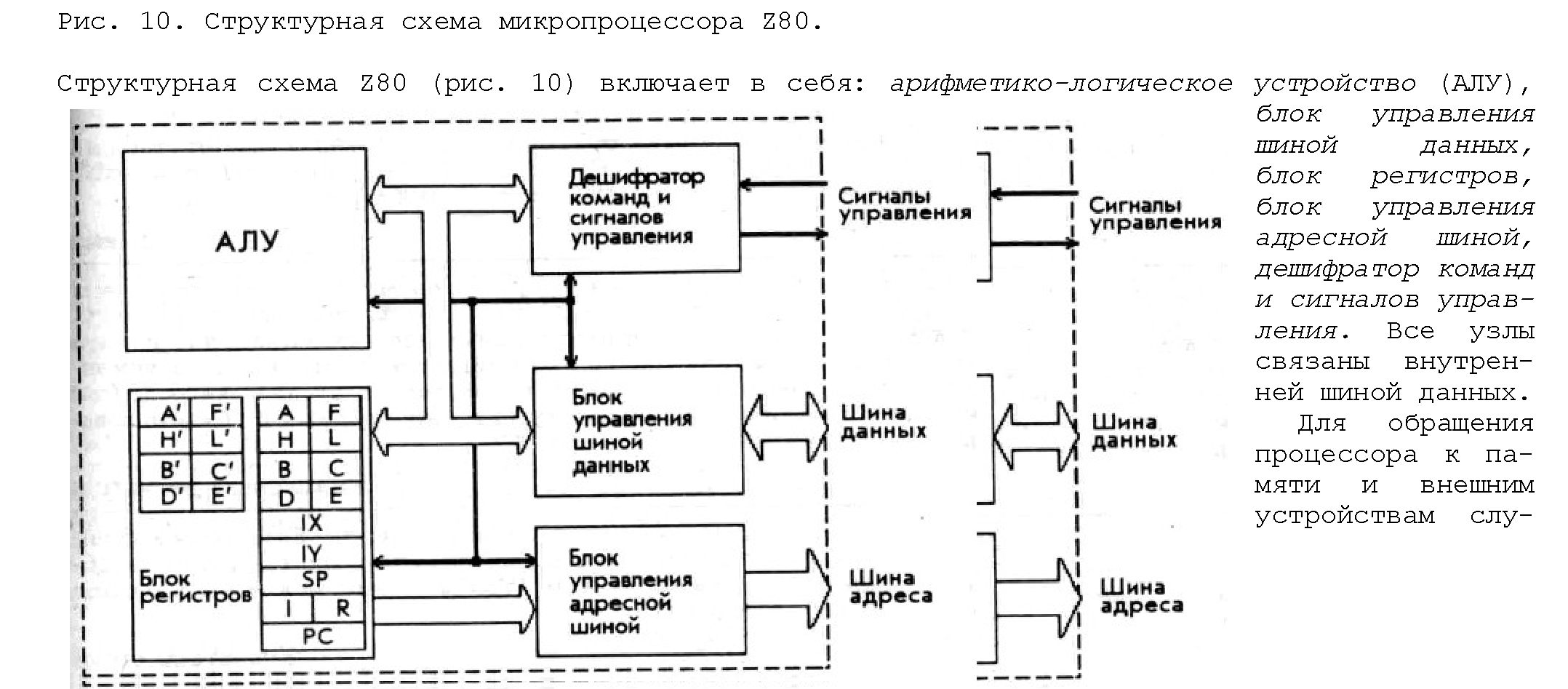

Структурная схема процессора:

Разъяснения к структурной схеме:

— ОП обычно не входит в состав МП и реализуется внешними схемами, но в небольших ЭВМ, ОЭВМ может совмещаться с ЦП.

— АЛУ процессора

выполняет логические, арифметические операции над данными. В МП может имеется

одно универсальное АЛУ для всех операций или несколько специальных АЛУ для

отдельных видов операций.

В МП может имеется

одно универсальное АЛУ для всех операций или несколько специальных АЛУ для

отдельных видов операций.

— УУ вырабатывает последовательность управляющих сигналов, инициирующих выполнение соответствующей последовательности микроопераций обеспечивающей реализацию текущей команды.

— Блок управляющих регистров предназначен для временного хранения управляющей информации. Он содержит регистры и счетчики, участвующие в управлении вычислительным процессом: состояние МП, регистр — счетчик адреса команды, счетчики тактов, регистр запросов прерываний.

— Блок регистровой памяти — местная память более высокого быстродействия чем ОП. Регистры этого блока служат для хранения операндов, в качестве аккумуляторов, базовых и индексных регистров, указателя стека.

— Блок связи с ОП организует обмен информацией процессора с ОП и защиту участков ОП от недозволенных данной программе обращений, а также связь МП с ПУ.

— Блок контроля и

диагностики служит для обнаружения сбоев и отказов в аппаратуре МП,

восстановление работы программы после сбоев и поиска места неисправности при

отказах.

|

|||

Общие сведения о настройке питания и производительности для Windows Server

- Чтение занимает 15 мин

Оцените свои впечатления

Да Нет

Хотите оставить дополнительный отзыв?

Отзывы будут отправляться в корпорацию Майкрософт. Нажав кнопку «Отправить», вы разрешаете использовать свой отзыв для улучшения продуктов и служб Майкрософт. Политика конфиденциальности.

Нажав кнопку «Отправить», вы разрешаете использовать свой отзыв для улучшения продуктов и служб Майкрософт. Политика конфиденциальности.

Отправить

Спасибо!

В этой статье

Эффективность энергопотребления в корпоративных средах и центрах обработки данных все равно важна, и она добавляет еще один набор компромиссов к сочетаниям параметров конфигурации. При управлении серверами важно убедиться, что они выполняются максимально эффективно, при этом удовлетворяют потребности в производительности рабочих нагрузок. Windows Server оптимизирован для обеспечения высокой эффективности энергопотребления с минимальным влиянием на производительность в самых разных рабочих нагрузках клиентов. настройка управления питанием процессора (система УПП) для схемы управления питанием с балансировкой Windows Server описывает рабочие нагрузки, используемые для настройки параметров по умолчанию в нескольких версиях Windows Server, а также предоставляет рекомендации по настройке.

В этом разделе разворачиваются компромиссы, помогающие принимать взвешенные решения, если необходимо изменить параметры управления питанием по умолчанию на сервере. однако большинство серверного оборудования и рабочих нагрузок не должны требовать настройки управления питанием администратора при работе Windows server.

Выбор метрик поворота

При настройке сервера для энергосбережения необходимо также учитывать производительность. Настройка влияет на производительность и энергопотребление, иногда в непропорциональной сумме. Для каждой возможной корректировки рассмотрите требования к бюджету питания и производительности, чтобы определить, приемлемо ли компромисс.

настройка параметров по умолчанию для Windows сервера использует экономичность энергии в качестве ключевой метрики для балансировки мощности и производительности. Эффективность энергопотребления — это отношение работы к среднему питанию, которое требуется в течение определенного периода времени.

Эту метрику можно использовать для установки практических целей, учитывающих компромисс между питанием и производительностью. В отличие от этого, цель экономии энергии в 10% в центре обработки данных не позволяет захватить соответствующие эффекты на производительность и наоборот.

В отличие от этого, цель экономии энергии в 10% в центре обработки данных не позволяет захватить соответствующие эффекты на производительность и наоборот.

Аналогичным образом, если настроить сервер для повышения производительности на 5%, что приводит к увеличению энергопотребления на 10 процентов, то общий результат может быть неприемлемым для ваших бизнес-целей. Метрика эффективности энергопотребления позволяет принимать более обоснованные решения, а не только метрики мощности или производительности.

Измерение энергопотребления системы

Прежде чем настраивать сервер для повышения эффективности энергопотребления, следует установить базовое измерение мощности.

если сервер имеет необходимую поддержку, можно использовать функции измерения и управления питанием в Windows Server 2016 для просмотра потребления энергии на уровне системы с помощью системного монитора.

один из способов определить, поддерживает ли ваш сервер отслеживание и бюджетирование, — просматривать каталог Windows server. если модель сервера соответствует новой расширенной квалификации по управлению питанием в программе Windows сертификации оборудования, гарантируется поддержка функций измерения и бюджетирования.

если модель сервера соответствует новой расширенной квалификации по управлению питанием в программе Windows сертификации оборудования, гарантируется поддержка функций измерения и бюджетирования.

Другой способ проверить поддержку отслеживания использования — вручную найти счетчики в системном мониторе. Откройте системный монитор, выберите Добавить счетчики, а затем найдите группу счетчиков индикатора питания .

Если в поле экземпляры выбранного объектаотображаются именованные экземпляры Power метры, ваша платформа поддерживает измерение. Счетчик питания , отображающий питание в ватт, отображается в выбранной группе счетчиков. Точное наследование значения данных о питании не указано. Например, это может быть мгновенное Рисование энергии или среднее энергопотребление за некоторый интервал времени.

Если серверная платформа не поддерживает измерение, можно использовать физическое устройство, подключенное к источнику питания, чтобы измерять энергопотребление системы или энергопотребление.

Чтобы установить базовый уровень, необходимо измерять среднюю мощность, необходимую для различных точек загрузки системы, от бездействия до 100% (максимальная пропускная способность) для создания линии загрузки. На следующем рисунке показаны линии загрузки для трех образцов конфигураций:

Строки загрузки можно использовать для оценки и сравнения производительности и потребления энергии конфигураций во всех точках загрузки. В этом конкретном примере можно легко увидеть, что такое лучшая конфигурация. Однако возможны ситуации, когда одна конфигурация лучше всего подходит для интенсивных рабочих нагрузок, и одна из них лучше всего подходит для облегченных рабочих нагрузок.

Чтобы выбрать оптимальную конфигурацию, необходимо тщательно разобраться в требованиях к рабочей нагрузке. Не следует думать, что при обнаружении хорошей конфигурации она всегда будет оптимальной. Вы должны измерять использование системы и энергопотребление на регулярной основе и после изменений рабочих нагрузок, уровней рабочей нагрузки или серверного оборудования.

Диагностика проблем с энергосбережением

PowerCfg.exe поддерживает параметр командной строки, который можно использовать для анализа эффективности сервера в неактивном энергопотреблении. При запуске PowerCfg.exe с параметром /енерги средство выполняет проверку 60-секунд для обнаружения потенциальных проблем с энергосбережением. Средство создает простой HTML-отчет в текущем каталоге.

Важно!

Чтобы обеспечить точный анализ, перед запуском PowerCfg.exeубедитесь, что все локальные приложения закрыты.

Сокращение частоты тактов таймера, драйверов, в которых отсутствует поддержка управления питанием и чрезмерное использование ЦП, — это несколько проблем поведения, обнаруженных командой powercfg/енерги . Это средство предоставляет простой способ обнаружения и устранения проблем управления питанием, что может привести к значительному снижению затрат в большом центре обработки данных.

Дополнительные сведения о PowerCfg. exe см. в разделе Параметры командной строки Powercfg.

exe см. в разделе Параметры командной строки Powercfg.

использование схем управления питанием в Windows Server

Windows Server 2016 имеет три встроенных плана управления питанием, разработанных для удовлетворения различных бизнес-потребностей. Эти планы предоставляют простой способ настройки сервера в соответствии с целями питания или производительности. В следующей таблице описаны планы, перечислены распространенные сценарии использования каждого плана и приведены некоторые сведения о реализации каждого плана.

| План | Описание | Распространенные применимые сценарии | Основные особенности реализации |

|---|---|---|---|

| Сбалансированный (рекомендуется) | Значение по умолчанию. Нацелены на экономичное энергопотребление с минимальным влиянием на производительность. | Общие вычисления | Соответствует емкости по запросу. Экономия энергии обеспечивает баланс мощности и производительности. |

| Высокая производительность | Повышение производительности за счет использования высокой энергии. Действуют ограничения по питанию и температуре, эксплуатационные расходы и надежность. | Приложения с низкой задержкой и код приложения, которые чувствительны к изменениям производительности процессора | Процессоры всегда блокируются с наибольшим состоянием производительности (включая частоты «Turbo»). Все ядра не будут приостановлены. Данные для термальной температуры могут быть значительными. |

| Экономия энергии | Ограничивает производительность для экономии энергии и снижения эксплуатационных расходов. Не рекомендуется без тщательного тестирования, чтобы обеспечить достаточную производительность. | Развертывания с ограниченными бюджетами питания и температурными ограничениями | Частота процессора с поддержкой CAPS в процентах от максимального (если поддерживается) и включает другие функции энергосбережения. |

эти схемы управления питанием существуют в Windows для чередующихся систем с питанием от сети и прямого тока (DC), но предполагается, что серверы всегда используют источник питания AC.

Дополнительные сведения о схемах управления питанием и конфигурациях политик питания см. в разделе Параметры командной строки Powercfg.

Примечание

Некоторые серверные производства имеют собственные возможности управления питанием, доступные в настройках BIOS. если операционная система не имеет контроля над управлением питанием, изменение схем управления питанием в Windows не повлияет на энергопотребление и производительность системы.

Настройка параметров управления питанием процессора

Каждая схема управления питанием представляет собой сочетание многочисленных параметров управления питанием. Встроенные планы — это три коллекции рекомендуемых параметров, охватывающие разнообразные рабочие нагрузки и сценарии. Однако мы понимаем, что эти планы не будут соответствовать потребностям каждого клиента.

В следующих разделах описаны способы настройки некоторых параметров управления питанием процессора в соответствии с целями, которые не были решены тремя встроенными планами. Если необходимо получить представление о более широком массиве параметров питания, см. раздел Параметры командной строки Powercfg.

Если необходимо получить представление о более широком массиве параметров питания, см. раздел Параметры командной строки Powercfg.

Intel управляется оборудованием P-States (ХВП)

начиная с процессоров intel Broadwell, использующих WS2016, Windows система УПП использует программное обеспечение intel, управляемое оборудованием P-states (хвп). ХВП — это новая возможность для совместного управления оборудованием и программной производительностью. Когда ХВП включен, ЦП наблюдает за работой и масштабируемостью и выбирает частоту в аппаратном масштабе времени. ОС больше не требуется для мониторинга активности и выбора частоты через равные промежутки времени. Переключение на ХВП имеет несколько преимуществ:

- Быстро отвечайте на пакетные рабочие нагрузки. Windows интервал проверки система УПП установлен как 30ms по умолчанию и может быть уменьшен как минимум до 15ms. Однако ХВП может настроить частоту на быстром уровне при каждом 1 мс.

- ЦП дает лучшие знания о производительности оборудования каждого состояния P.

Это позволяет лучше выбрать частоту процессора для достижения максимальной эффективности энергопотребления.

Это позволяет лучше выбрать частоту процессора для достижения максимальной эффективности энергопотребления. - ЦП может использовать другие аппаратные возможности, например память, GPU и т. д., в учетную запись для достижения максимальной эффективности работы при определенных TDPах (тепловой мощности).

Windows может по-прежнему устанавливать минимальное и максимальное состояния процессора, чтобы ограничить диапазон частот, которые могут выполняться процессорами. Кроме того, он может установить следующий параметр политики настройки производительности энергопотребления процессора (EPP), чтобы указать ХВП в качестве приоритета для мощности или производительности.

- Политика настройки производительности энергопотребления процессора для установки баланса между питанием и производительностью. Чем меньше значение, тем выше производительность, а более высокое значение — преимущество. Значение может находиться в диапазоне от 0 до 100. Значение по умолчанию 50, которое используется для балансировки мощности и производительности.

Приведенные ниже команды уменьшают значение EPP до 0 в текущей схеме управления питанием, чтобы полностью повысить производительность по сравнению с энергопотреблением.

Powercfg -setacvalueindex scheme_current sub_processor PERFEPP 0

Powercfg -setactive scheme_current

Минимальное и максимальное состояние производительности процессора

Процессоры меняются между состояниями производительности (P-состояния) очень быстро, чтобы соответствовать спросу, обеспечивая производительность по мере необходимости и экономию энергии, когда это возможно. Если сервер имеет определенные высокопроизводительные или минимальные требования к энергопотреблению, можно подумать о настройке минимального значения параметра состояния производительности процессора или параметра состояния максимальной производительности процессора .

Значения минимального состояния производительности процессора и максимального состояния производительности процессора выражаются в процентах от максимальной частоты процессора и значения в диапазоне от 0 до 100.

Если сервер требует высокой задержки, неизменяемой частоты ЦП (например, для повторяемого тестирования) или наивысшего уровня производительности, процессоры могут переключаться на более низкие состояния производительности. Для такого сервера можно ограничить минимальное состояние производительности процессора на 100% с помощью следующих команд:

Powercfg -setacvalueindex scheme_current sub_processor PROCTHROTTLEMIN 100

Powercfg -setactive scheme_current

Если сервер требует снижения энергопотребления энергии, может потребоваться закрепление состояния производительности процессора в процентах от максимума. Например, можно ограничить процессор до 75% от максимальной частоты с помощью следующих команд:

Powercfg -setacvalueindex scheme_current sub_processor PROCTHROTTLEMAX 75

Powercfg -setactive scheme_current

Примечание

При ограничении производительности процессора в процентах от максимума требуется поддержка процессора. Проверьте документацию по процессору, чтобы определить, существует ли такая поддержка, или просмотрите счетчик производительности » % максимальной частоты » в группе » процессор «, чтобы узнать, были ли применены какие либо ограничения по частоте.

Проверьте документацию по процессору, чтобы определить, существует ли такая поддержка, или просмотрите счетчик производительности » % максимальной частоты » в группе » процессор «, чтобы узнать, были ли применены какие либо ограничения по частоте.

Переопределение скорости реагирования процессора

Алгоритмы управления питанием на основе использования ЦП обычно используют среднюю загрузку ЦП в окне проверки времени, чтобы определить, нужно ли увеличивать или уменьшать частоту. Это может отрицательно понизить задержку дисковых операций ввода-вывода или интенсивных сетевых нагрузок. Логический процессор может быть бездействующим при ожидании завершения дискового ввода-вывода или сетевых пакетов, что приводит к нехватке общего использования ЦП. В результате Управление питанием будет выбирать низкую частоту для этого процессора. Эта проблема существует и в управлении питанием на основе ХВП. DPC и потоки, обрабатывающие завершение операций ввода-вывода или сетевые пакеты, находятся в критическом пути и не должны выполняться с низкой скоростью. чтобы устранить эту проблему, Windows система УПП учитывает число dpc. если число DPC превышает определенный порог в прошлом окне мониторинга, система УПП введет период скорости реагирования ввода-вывода и порождает частоту, связанную с более высоким уровнем. Такт частоты будет сброшен, когда число DPC достаточно мало для некоторого времени. Поведение может быть настроено с помощью следующих параметров.

чтобы устранить эту проблему, Windows система УПП учитывает число dpc. если число DPC превышает определенный порог в прошлом окне мониторинга, система УПП введет период скорости реагирования ввода-вывода и порождает частоту, связанную с более высоким уровнем. Такт частоты будет сброшен, когда число DPC достаточно мало для некоторого времени. Поведение может быть настроено с помощью следующих параметров.

| Параметр | Описание | Значение по умолчанию | Минимальное значение | Максимальное значение |

|---|---|---|---|---|

| Переопределение включения скорости реагирования процессора | Число DPC в рамках проверки производительности, выше которых должны быть включены переопределения скорости реагирования процессора | 10 | 0 | Недоступно |

| Переопределение порогового значения отключения процессора | Число DPC в рамках проверки производительности, по которой следует отключить переопределение скорости реагирования процессора | 5 | 0 | Недоступно |

| Переопределение времени реагирования процессора | Число последовательных проверок производительности, которые должны соответствовать пороговому значению включения до включения переопределений скорости реагирования процессора | 1 | 1 | 100 |

| Время отключения процессора — переопределение | Число последовательных проверок производительности, которые должны соответствовать пороговому значению отключения до отключения переопределений скорости реагирования процессора | 3 | 1 | 100 |

| Основание производительности при отклике процессора | Минимальная допустимая производительность процессора при включенных переопределениях скорости реагирования процессора | 100 | 0 | 100 |

| Повышение скорости реагирования процессора переопределение настроек производительности энергии | Значение политики максимального приоритета энергии, если переопределение скорости реагирования процессора включено | 100 | 0 | 100 |

Например, если Рабочая нагрузка сервера не чувствительна к задержке и требуется освободить переопределение скорости реагирования, можно увеличить переопределение скорости реагирования процессора, а также разрешить переопределение скорости реагирования процессора, уменьшить пороговое значение отключения процессора и переопределить время отклика процессора. После этого система будет трудно ввести в состояние переопределение отклика. Значение по умолчанию для счетчика производительности «время реагирования процессора» задается как 100, так что период переопределения скорости реагирования будет выполняться с максимальной частотой. Кроме того, можно уменьшить производительность процессора и уменьшить скорость реагирования процессора, чтобы позволить ХВП настраивать частоту. Ниже приведены примеры команд для задания параметров текущей активной схемы управления питанием.

После этого система будет трудно ввести в состояние переопределение отклика. Значение по умолчанию для счетчика производительности «время реагирования процессора» задается как 100, так что период переопределения скорости реагирования будет выполняться с максимальной частотой. Кроме того, можно уменьшить производительность процессора и уменьшить скорость реагирования процессора, чтобы позволить ХВП настраивать частоту. Ниже приведены примеры команд для задания параметров текущей активной схемы управления питанием.

Powercfg -setacvalueindex scheme_current sub_processor RESPENABLETHRESHOLD 100

Powercfg -setacvalueindex scheme_current sub_processor RESPDISABLETHRESHOLD 1

Powercfg -setacvalueindex scheme_current sub_processor RESPENABLETIME 10

Powercfg -setacvalueindex scheme_current sub_processor RESPDISABLETIME 1

Powercfg -setacvalueindex scheme_current sub_processor RESPPERFFLOOR 5

Powercfg -setacvalueindex scheme_current sub_processor RESPEPPCEILING 50

Powercfg -setactive scheme_current

Режим повышения производительности процессора

Эта настройка параметров применяется только к системам, не являющимся ХВП.

Технологии Intel Turbo Boost и AMD Turbo CORE — это функции, позволяющие процессорам добиться дополнительной производительности, когда она наиболее полезна (то есть при высоких нагрузках на систему). однако эта функция увеличивает энергопотребление цп, поэтому Windows Server 2016 настраивает технологии Turbo на основе используемой политики электропитания и конкретной реализации процессора.

Для высокопроизводительных схем управления питанием на всех процессорах Intel и AMD включена поддержка Turbo, и для них отключены схемы Power энергосберегающая. Для сбалансированных схем управления питанием в системах, основанных на традиционном управлении частотой, основанной на состоянии P-состояния, Turbo включается по умолчанию, только если платформа поддерживает Регистр ЕПБ.

Примечание

Регистр ЕПБ поддерживается только в процессорах Intel Вестмере и более поздних версий.

Для процессоров Intel Нехалем и AMD по умолчанию Turbo отключено на платформах, основанных на состоянии P-State. однако, если система поддерживает управление производительностью совместного использования процессора (кппк), то есть новый альтернативный режим взаимодействия между операционной системой и оборудованием (определенный в ACPI 5,0), можно использовать Turbo, если Windows операционная система динамически запрашивает оборудование для обеспечения максимального числа возможных уровней производительности.

однако, если система поддерживает управление производительностью совместного использования процессора (кппк), то есть новый альтернативный режим взаимодействия между операционной системой и оборудованием (определенный в ACPI 5,0), можно использовать Turbo, если Windows операционная система динамически запрашивает оборудование для обеспечения максимального числа возможных уровней производительности.

Чтобы включить или отключить функцию Turbo Boost, параметр режима повышения производительности процессора должен быть настроен администратором или параметрами по умолчанию для выбранной схемы управления питанием. Режим повышения производительности процессора имеет пять допустимых значений, как показано в таблице 5.

Для элементов управления на основе P-состояния варианты отключаются, включаются (устройство Turbo доступно оборудованию при запросе номинальной производительности) и эффективно (Turbo доступно только при реализации регистра ЕПБ).

для элемента управления на основе кппк варианты отключаются, эффективность включена (Windows указывает точный объем быстрого доступа) и агрессивный (Windows запрашивает максимальную производительность, чтобы включить Turbo).

в Windows Server 2016 значение по умолчанию для режима усиления — 3.

| имя; | Поведение на основе P-состояния | Поведение КППК |

|---|---|---|

| 0 (отключено) | Выключено | Выключено |

| 1 (включено) | Активировано | Эффективность включена |

| 2 (агрессивно) | Включен | Aggressive |

| 3 (эффективность включена) | Эффективно | Эффективность включена |

| 4 (эффективный агрессивный) | Эффективно | Aggressive |

Следующие команды включают режим повышения производительности процессора в текущей схеме управления питанием (укажите политику с помощью псевдонима GUID):

Powercfg -setacvalueindex scheme_current sub_processor PERFBOOSTMODE 1

Powercfg -setactive scheme_current

Важно!

Чтобы включить новые параметры, необходимо выполнить команду powercfg-сетактиве . Перезагружать сервер не требуется.

Перезагружать сервер не требуется.

Чтобы задать это значение для схем управления питанием, отличных от текущего выбранного плана, можно использовать псевдонимы, такие как SCHEME_MAX (экономия энергии), SCHEME_MIN (высокая производительность) и SCHEME_BALANCED (сбалансированная) вместо SCHEME_CURRENT. Замените «схема Current» в командах Powercfg-сетактиве, которые ранее отображались с нужным псевдонимом, чтобы включить эту схему управления питанием.

Например, чтобы настроить режим усиления в плане экономии энергии и сделать его текущим планом, выполните следующие команды:

Powercfg -setacvalueindex scheme_max sub_processor PERFBOOSTMODE 1

Powercfg -setactive scheme_max

Увеличение производительности процессора и снижение пороговых значений и политик

Эта настройка параметров применяется только к системам, не являющимся ХВП.

Скорость, с которой увеличивается или уменьшается состояние производительности процессора, управляется несколькими параметрами. Следующие четыре параметра имеют наиболее заметные последствия:

Порог увеличения производительности процессора определяет значение использования, по достижении которого увеличится состояние производительности процессора. Большие значения снижают скорость увеличения состояния производительности в ответ на повышенные действия.

Порог уменьшения производительности процессора определяет значение использования, ниже которого будет снижаться состояние производительности процессора. Большие значения увеличивают скорость уменьшения состояния производительности во время периодов простоя.

Производительность процессора увеличение политики и снижение производительности процессора Политика определяет, какое состояние производительности должно быть задано при изменении. Политика «Single» означает, что она выбирает следующее состояние. «Rocket» — максимальное или минимальное состояние производительности электропитания. «Идеальный вариант» пытается найти баланс между питанием и производительностью.

Например, если сервер требует высокой задержки, при этом вы по-прежнему захотите воспользоваться преимуществами низкого энергопотребления в периодах простоя, то можно было бы увеличить состояние производительности для любого увеличения нагрузки и замедлить уменьшение времени, когда нагрузка выйдет из строя. Следующие команды устанавливают для политики увеличения значение «Rocket» для ускорения увеличения состояния и устанавливают для политики уменьшения значение «Single». Пороговые значения увеличения и уменьшения задаются равными 10 и 8 соответственно.

Powercfg.exe -setacvalueindex scheme_current sub_processor PERFINCPOL 2

Powercfg.exe -setacvalueindex scheme_current sub_processor PERFDECPOL 1

Powercfg.exe -setacvalueindex scheme_current sub_processor PERFINCTHRESHOLD 10

Powercfg.exe -setacvalueindex scheme_current sub_processor PERFDECTHRESHOLD 8

Powercfg.exe /setactive scheme_current

Максимальное и минимальное число ядер для ядер производительности процессора

стоянка ядер — это функция, появившаяся в Windows Server 2008 R2. подсистема управления питанием процессора (система УПП) и планировщик работают вместе для динамического регулирования количества ядер, доступных для выполнения потоков. подсистема система УПП выбирает минимальное количество ядер для потоков, которые будут запланированы.

Для ядер, которые приостановлены, обычно не запланировано ни одного потока, и они будут переведены в очень низкие состояния питания, если они не обрабатывают прерывания, DPC или другие строго привязаны работы. Остальные ядра отвечают за оставшуюся часть рабочей нагрузки. Стоянка ядер потенциально может повысить эффективность энергопотребления во время пониженного использования.

Для большинства серверов поведение ядра по умолчанию обеспечивает разумное распределение пропускной способности и энергии. На процессорах, где стоянка ядра может не показывать как можно больше преимуществ универсальных рабочих нагрузок, по умолчанию она может быть отключена.

Если сервер имеет определенные основные требования к стоянке, можно управлять количеством ядер, доступных для приостановки, с помощью параметра максимального числа ядер ядра производительности процессора или параметра «минимальное число ядер ядра производительности процессора » в Windows Server 2016.

Один из сценариев, в котором основная стоянка не всегда оптимальна для, — когда один или несколько активных потоков привязаны к нетривиальному подмножеству ЦП узла NUMA (то есть более 1 ЦП, но меньше, чем весь набор ЦП на узле). Когда основной алгоритм стоянки выполняет комплектацию ядер для освобождения (при условии увеличения интенсивности рабочей нагрузки), он может не всегда выбирать ядра в активном подмножестве привязаны (или подмножествах) для освобождения, что может привести к неприпаркованным ядрам, которые фактически не используются.

Значения этих параметров задаются в процентах в диапазоне от 0 до 100. Параметр максимального числа ядер ядра производительности процессора управляет максимальным процентом ядер, которые могут быть неприпаркованными (доступными для выполнения потоков) в любое время, в то время как параметр минимального числа ядер ядра производительности процессора управляет минимальным процентом ядер, которые могут быть неприпаркованными. Чтобы отключить приостановка ядра, задайте для параметра минимального количества ядер ядра производительности процессора значение 100% с помощью следующих команд:

Powercfg -setacvalueindex scheme_current sub_processor CPMINCORES 100

Powercfg -setactive scheme_current

Чтобы уменьшить количество планируемых ядер до 50% от максимального значения счетчика, задайте для параметра Максимальная доля ядер ядра производительности процессора значение 50 следующим образом:

Powercfg -setacvalueindex scheme_current sub_processor CPMAXCORES 50

Powercfg -setactive scheme_current

Распространение служебной программы парковки ядра производительности процессора

распространение служебной программы — это алгоритм оптимизации в Windows Server 2016, предназначенный для повышения эффективности энергопотребления для некоторых рабочих нагрузок. Он отслеживает неперемещаемую активность ЦП (то есть DPC, прерываний или строго привязаны потоков) и прогнозирует будущую работу на каждом процессоре в зависимости от предположения, что любая перемещаемая работа может равномерно распределяться по всем неприпаркованным ядрам.

Распространение служебной программы включено по умолчанию для сбалансированной схемы управления питанием для некоторых процессоров. Это позволяет сократить энергопотребление процессора, уменьшая запрошенные частоты ЦП рабочих нагрузок, которые находятся в определенном стабильном состоянии. Однако распространение служебной программы не обязательно является хорошим выбором алгоритма для рабочих нагрузок, для которых накладываются высокие объемы действий или для программ, в которых Рабочая нагрузка быстро и случайно смещается между процессорами.

Для таких рабочих нагрузок рекомендуется отключить распространение служебной программы с помощью следующих команд:

Powercfg -setacvalueindex scheme_current sub_processor DISTRIBUTEUTIL 0

Powercfg -setactive scheme_current

Дополнительные ссылки

Архитектура процессора Intel 80486 – схема, регистры

КомпьютерПресс №3 1993. А. Борзенко

Интегральная схема микропроцессора i80486 была анонсирована фирмой Intel в 1989 году на выставке Comdex в Чикаго. И хотя, очевидно, нам не долго уже осталось ждать появления нового 586-го микропроцессора, на сегодняшний день одним из самых мощных универсальных микропроцессоров является i80486.

Архитектура микропроцессора i80486

«В архитектуре взаимосвязаны функциональные, технические и эстетические

начала — польза, прочность, красота».

(Из словаря)

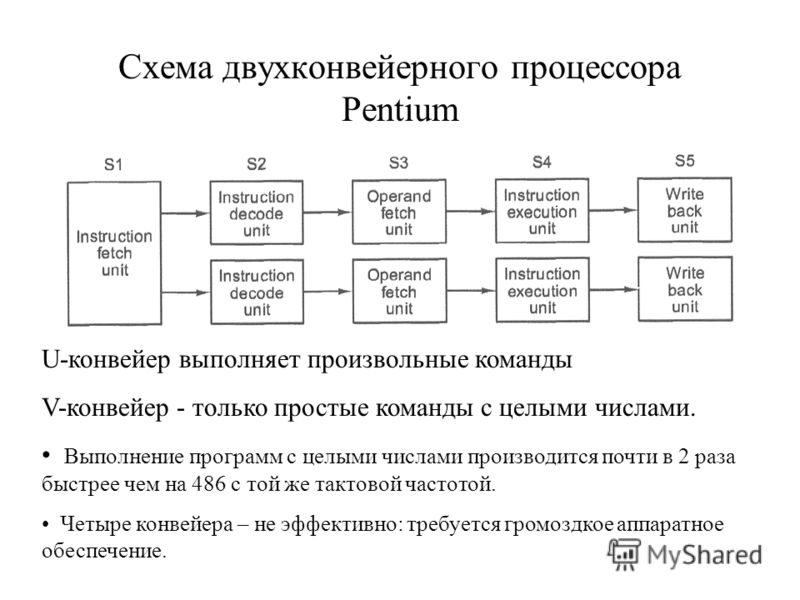

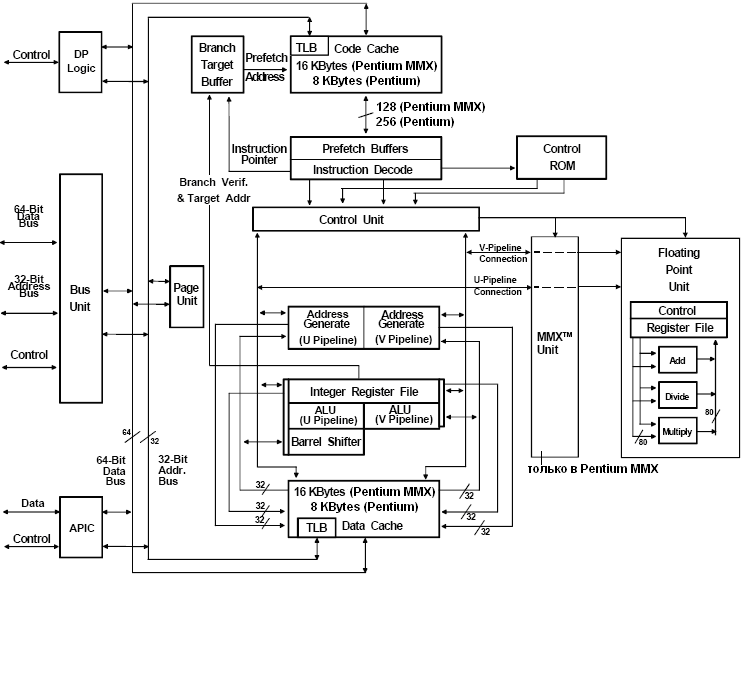

Микропроцессор i80486 достойный продолжатель семейства i80x86‚ поскольку он позволяет создавать вычислительные системы намного более производительные, чем, предположим, на микропроцессоре i80386. В принципе микросхема i80486 состоит из полного микропроцессора i80386, арифметического сопроцессора i80387 и контроллера кэш-памяти i82385. Понятно, что речь не идет о механическом соединении функциональных устройств на одном кристалле. Высокая степень интеграции (более миллиона транзисторов) — это не просто технологическое достижение, а возможность реализовать новые архитектурные решения, которые позволяют повысить производительность микропроцессора. Так, например, в микропроцессоре i80486 используется конвейерная обработка команд, достаточно широко применяемая в RISC-процессорах. При одной и той же тактовой частоте с i80386 микропроцессор i80486 работает в три-четыре раза производительнее. Это связано с уменьшением количества циклов (тактов), необходимых для выполнения команды (инструкции).

Три в одном

На рис. 1 приведена примерная блок-схема микропроцессора i80486, на которой достаточно легко выделить его основные функциональные узлы — устройство управления памятью (Memory Management Unit, MMU), модуль арифметического сопроцессора (Floating Point Unit, FPU) и блок кэш-памяти (Cache Unit). Несмотря на то, что микропроцессор i80486 обладает всеми свойствами, присущими i80386, имеются, конечно, и различия. Например, в набор команд микропроцессора i80486 наряду с известными инструкциями для i80386, включено несколько дополнительных команд. Однако устройство управления памятью MMU полностью совместимо с аналогичным устройством в i80386. То же можно сказать и о FPU. А это, вообще говоря, означает, что все программное обеспечение, работающее на серии микропроцессоров 80×86/80×87, без внесения каких-либо изменений будет работать и на i80486.

Рис. 1. Блок-схема микропроцессора 80486 увеличить рисунокУстройство управления памятью MMU состоит в свою очередь из устройства сегментации (Segmentation Unit) и устройства управления страницами (Paging Unit). Благодаря делению памяти на сегменты (сегментации) коды программ и области данных могут находиться практически в любом месте логического адресного пространства. Иными словами, при сегментной организации памяти каждый модуль занимает свою собственную сплошную область памяти, тогда как при страничной организации модуль разбивается на отдельные страницы. В свою очередь, устройство управления страницами позволяет реализовать механизм страничной организации памяти, который функционирует на более низком уровне и является прозрачным по отношению к процессу сегментации. Это дает возможность управления физическим адресным пространством. Следует также отметить, что страничная организация памяти (paging) может быть отключена чисто программным способом.

Каждый сегмент памяти может подразделяться на один или несколько 4-Кбайтных блоков. А память, в свою очередь, может быть организована в виде одного или нескольких таких сегментов, размер которых может достигать 4 Гбайт. Причем каждому такому сегменту могут придаваться соответствующие атрибуты, которые определяют его расположение в памяти, величину, вид (стек, код, данные) и характеристику защиты. Каждая задача, выполняемая на i80486, может в принципе состоять из 16 381 сегмента, по 4 Гбайта каждый. Таким образом, диапазон виртуальной адресации достигает 64 Тбайт. Устройство сегментации микропроцессора поддерживает четыре механизма защиты приложений и системного режима друг от друга. Благодаря этому на базе микропроцессора i80486 возможно построение высокозащищенных систем.

Принципиально микропроцессор i80486 имеет два режима работы: реальный режим (Real Mode, иначе 8086-Mode) и защищенный (Protected Mode). При этом в реальном режиме он ведет себя просто как очень быстрый микропроцессор i8086. Из этого режима i80486 может легко переключиться в защищенный режим, в котором имеются богатые возможности управления памятью. Например, в этом режиме возможно переключение с одной задачи на другую, причем их обработка будет происходить как обработка независимых задач на своих i8086 микропроцессорах (режим «виртуальных 8086-машин»). Такое название связано с тем, что каждая задача ведет себя таким же образом, как если бы она выполнялась на собственном процессоре i8086 (соответственно i8088).

Устройство арифметического сопроцессора в i80486 работает параллельно с АЛУ и поддерживает большое количество арифметических команд для различных типов операндов. Это, в частности, многочисленные трансцендентные функции, такие как синус, косинус, тангенс, логарифм и т.д. Нужно отметить, что FPU полностью поддерживает стандарт ANSI/IEEE 754-1985 на арифметические операции с плавающей точкой.

Размер внутренней кэш-памяти микропроцессора i80486 составляет 8 Кбайт. Сразу следует сказать, что для некоторых приложений такой размер кэш-памяти вовсе не достаточен. Это касается в первую очередь САПР и настольных издательских систем. Однако в этом случае при разработке соответствующей системы можно воспользоваться кэш-контроллером i82485 и внешней кэш-памятью объемом 64 или 128 Кбайт. Внутренняя кэш-память выполнена как ассоциативная и работает в режиме write through (то есть данные заносятся одновременно и в кэш-память, и в ОЗУ). Кэш в микропроцессоре i80486, безусловно, имеет и некоторые особенности. В частности, страницы памяти могут быть обозначены либо как «кэшируемые», либо как «некэшируемые», причем такое обозначение можно вводить как аппаратно, так и программно. Впрочем, даже само устройство кэша может быть также отключено как аппаратно, так и программно. По некоторым оценкам, использование встроенной кэш-памяти экономит до 80% времени, необходимого для обращения к ОЗУ.

Регистры, регистры, регистры…

Микропроцессор i80486 содержит, конечно, все регистры, имеющиеся в микросхемах i80386 и i80387. Регистры рассматриваемого микропроцессора можно условно подразделить на три большие группы: базовые регистры, регистры системного уровня и регистры плавающей точки. Рассмотрим эти группы регистров несколько подробнее.

Программная модель i80486 определяется главным образом базовыми регистрами, которые приведены на рис. 2. Это — восемь 32-разрядных регистров общего назначения, которые могут работать с операндами данных размерами 1, 2 и 4 байта или полями бит от 1 до 32. Однако операнды адреса могут иметь длину только либо 2, либо 4 байта. Эти 32-разрядные регистры обозначаются как EAX, EBX, ECX, EDX, ESI, EDI, EBP и ESP. Обозначения двух младших байт этих регистров пользователям микропроцессоров i8088/86/286 уже хорошо известны. Конечно, это — AX, BX, CX, DX, SI, DI, BP и SP. Причем следует отметить, что при доступе к старшим двум байтам этих 32-разрядных регистров содержимое двух младших байтов не изменяется. Этим обуславливается совместимость сверху-вниз с микропроцессором i80286. Операции с байтовыми операндами (старший и младший байты) доступны только для четырех регистров AX, BX, CX, DX, причем старшие байты соответствуют обозначениям AH, BH, CH и DH, а младшие — AL, BL, CL и DL.

Рис. 2. Регистры 80486Регистр указателя команд (Instruction Pointer, EIP) — также 32-разрядный и указывает на следующую выполняемую команду, конечно же, косвенно. Этот регистр указывает только смещение относительно начала кодового сегмента адреса, который образуется с использованием содержимого регистра CS и элемента дескрипторной таблицы (подробнее об этом несколько позже). Два младших байта регистра EIP соответствую 16-разрядному регистру IP, который используется только при 16-битной адресации.

Для обозначения базового 32—разрядного регистра побитной индикации состояния процессора используется так называемый регистр флагов — EFLAGS. Этот регистр содержит биты, характеризующие последнюю выполненную процессором операцию, и некоторую другую служебную информацию. На рис. 3 приведены обозначения битов в регистре EFLAGS. Поясним назначение некоторых из них. Если в регистре EFLAGS установлен 17-й бит — VM (Virtual 8086 Mode), то микропроцессор i80486 переходит в режим «виртуальных 8086-машин». Конечно, это возможно только в защищенном режиме. Бит 16 — RF (Resume Flag) используется обычно для отладочных режимов. При его установке прерывание, вызванное фатальной ошибкой, игнорируется и выполняется переход на следующую инструкцию. Бит 14 — NT (Nested Task) используется в i80486 для наблюдения за несколькими прерванными или вызванными по инструкции CALL программами. Два бита 12 и 13 IOPL (Input/Output Privilege Level) определяют право доступа в защищенном режиме к инструкциям ввода-вывода.

Рис. 3. Биты регистра EFLAGSИз шести 16-разрядных сегментных регистров четыре (DS, ES, FS и GS) называются регистрами сегментов данных, CS — регистром кодового сегмента, а SS — регистром сегмента стека. Как работают эти регистры в режиме микропроцессора i8086, достаточно хорошо известно. Для получения 20-разрядного физического адреса необходимо суммировать 16-битное смещение с базовым адресом, хранящимся в одном из сегментных регистров. Причем сложение происходит так, что содержимое сегментного регистра сдвинуто относительно второго слагаемого (смещения) влево на 4 разряда. То есть, по сути, происходит сложение 20-битового базового адреса (4 младших разряда которого, безусловно, всегда нули) с 16-битовым смещением, в результате, конечно, получается необходимый 20-разрядный адрес. При работе же микропроцессора i80486 (ну и, разумеется, i80386) в защищенном режиме исполнительный физический адрес образуется несколько иначе. Можно сказать, что он образуется из пяти компонент. Прежде всего отметим, что в защищенном режиме сегментные регистры называются селекторными, или просто селекторами. Селекторный регистр указывает на соответствующий элемент в одной из Дескрипторных Таблиц, расположенных в памяти. Причем базовый адрес этой Таблицы хранится либо в регистре Глобальной Дескрипторной Таблицы, либо в регистре Локальной Дескрипторной Таблицы, хотя в общем случае может храниться и в ином регистре микропроцессора. Каждый элемент Дескрипторной Таблицы содержит базовый адрес определенного сегмента, его величину и права доступа. У i80486 элемент Глобальной Дескрипторной Таблицы имеет размер 8 байт и состоит из 32-разрядного базового адреса, 20-разрядного поля размера сегмента и атрибутов дескриптора. В поле размера сегмента, например, может храниться либо количество байт (до 1 Мбайта), которое содержит данный сегмент, либо количество страниц по 4096 байт каждая. Следовательно, размер сегмента в защищенном режиме может варьироваться от 1 байта до 4 Гбайт. Таким образом, результирующий адрес в защищенном режиме может быть образован в общем случае суммированием содержимого базового регистра с содержимым индексного регистра, умноженного на масштабный коэффициент (1, 2, 4 или 8), плюс смещение в самой команде и плюс базовый адрес сегмента из элемента Дескрипторной Таблицы (рис. 4).

Рис. 4. Формирование адреса в защищенном режимеМикропроцессор i80486 имеет три управляющих регистра (Control Registers) системного уровня — CR0, CR2, и CR3 (регистр CR1 зарезервирован фирмой Intel для дальнейшего расширения). В регистре CR0 из имеющихся 32 бит для целей управления и определения статуса используется только 10 (рис. 5). Причем 5 из этих 10 бит появились только в i80486 (в i80386 их нет). Это биты — CD, NW, AM, WP и NE. Функционально все эти 10 бит характеризуют следующее: режимы микропроцессора i80486 — PG, PE, режимы встроенного устройства кэш-памяти — CD, NW, встроенное устройство управления плавающей арифметикой — TS, EM, MP и NE, управление контролем выравнивания — AM, защита записи супервизора — WP. Младшее слово регистра CR0 используется также в качестве статусного слова (слова состояния) микропроцессора (Machine Status Word, MSW), для того чтобы сохранить совместимость с защищенным режимом i80286. Следовательно, команды LMSW и SMSW (Load MSW, Store MSW) действуют только для нижних 16 бит CR0 и игнорируют новые биты. Для того чтобы можно было работать с этими новыми битым, в набор команд микропроцессора i80486 включена специальная инструкция MOV CR0, Reg.

Рис. 5. Регистр CR0В управляющем регистре CR2 накопится адрес, по которому появилась ошибка при разбиении памяти на страницы. Управляющий регистр CR3 используется только тогда, когда в регистре CR0 установлен бит PG. В этом случае регистр содержит базовый адрес таблицы страниц, которые может использовать микропроцессор для каждой задачи. Сама же эта таблица всегда выровнена на одну страницу (4 Кбайт).

Четыре адресных системных регистра в микропроцессорах i80386/486 используются для таблиц или сегментов, которые хранятся в основной памяти. Это — Глобальная Дескрипторная Таблица (Global Descriptor Table, GDT), Локальная Дескрипторная Таблица (Local Descriptor Table, LDT), Дескрипторная Таблица Прерываний (Interrupt Descriptor Table, IDT) и Сегмент Состояния Задачи (Task State Segment, TSS). Для обозначений соответствующих регистров используются аббревиатуры — GDTR, LDTR, IDTR и TR. Регистры GDTR и IDTR содержат 32-разрядный базовый адрес, а также 16-разрядную границу для таблиц GDT и IDT. Таблицы GDT и IDT находятся в распоряжении всех задач как глобальные сегменты, в то время как LDT и TSS зависят от конкретной задачи. В регистрах LDTR и TR хранятся 16-разрядные селекторы для выбора LDT и соответственно TSS-дескриптора.

Набор регистров для операций с плавающей точкой включает в себя восемь 80-разрядных регистров данных, 48-разрядные указатели данных и команд, а также 16-разрядные регистры управления, состояния и слова признаков. Поскольку принцип работы FPU полностью соответствует работе i80387, а арифметические сопроцессоры — хорошая тема для отдельного разговора, подробно останавливаться на эти регистрах мы пока не будем.

В следующих выпусках нашего журнала мы обязательно вернемся к разговору о микропроцессорах фирмы Intel, и не только о них.

А. Борзенко

КомпьютерПресс 3’92

См. также описание семейства процессоров x86.

Персональный сайт — Обобщенная схема центрального процессора

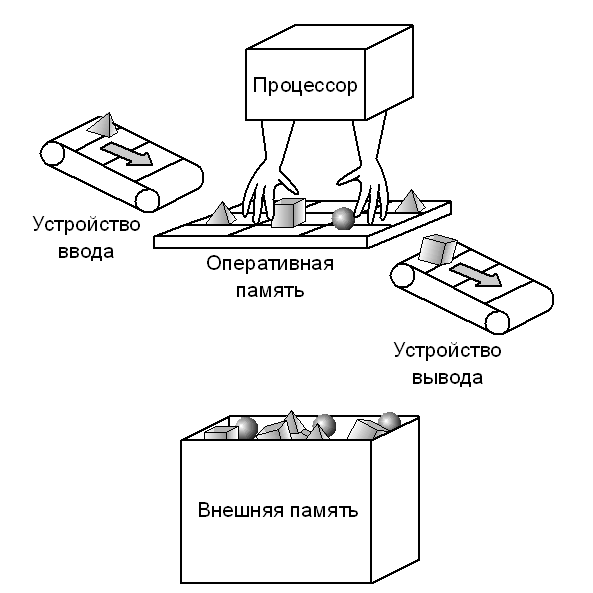

Краткое напоминание о фоннеймановской архитектуре (модели) ЭВМЧтобы получить представление о структуре и функциях процессора, обратимся к схеме гипотетической ЭВМ, модель которой традиционно называют фоннеймановской (рис. 24.1).

Рис. 24.1. Структурная схема гипотетической ЭВМ

Устройство управления (УУ) организует автоматическое выполнение

программ и функционирование ЭВМ как единой системы. Основная задача УУ

– выработка управляющих сигналов (УС) и распределение их по цепям

управления.

Арифметическологическое устройство (АЛУ) предназначено для выполнения

арифметических и логических операций над поступающими в него данными.

Оперативная память (ОП) представляет собой массив запоминающих

элементов (ЗЭ), организованных в виде ячеек, способных хранить некую

единицу информации.

Процессором называется функциональная часть ЭВМ, предназначенная для

непосредственного осуществления процесса преобразования (обработки)

информации и управления этим процессом. Другими словами – это

совокупность арифметическологического устройства и устройства

управления.

На рис. 24.2 приведена функциональная структура гипотетического процессора.

Рис. 2.2. Структура гипотетического процессора

Регистр адреса

Регистр адреса (РА) предназначен для хранения адреса ячейки основной

памяти вплоть до завершения операции (считывание или запись) с этой

ячейкой.

Указатель стека

Указатель стека (УкС) — это регистр, где хранится адрес вершины стека.

В реальных вычислительных машинах стек реализуется в виде участка

основной памяти обычно расположенного в области наибольших адресов.

Заполнение стека происходит в сторону уменьшения адресов, при этом

вершина стека — это ячейка, куда была произведена последняя по времени

запись. Для хранения адреса такой ячейки и предназначен УкС. При

выполнении операции занесения в стек содержимое УкС сначала уменьшается

на единицу, после чего используется в качестве адреса, по которому

производится запись. Соответствующая ячейка становится новой вершиной

стека. Считывание из стека происходит из ячейки, на которую указывает

текущий адрес в УкС, после чего содержимое указателя стека

увеличивается на единицу. Таким образом, вершина стека опускается, а

считанное слово считается удаленным из стека. Хотя физически считанное

слово и осталось в ячейке памяти, при следующей записи в стек оно будет

заменено новой информацией.

Счетчик команд

Счетчик команд (СК) — неотъемлемый элемент процессора любой ЭВМ,

построенной в соответствии с фоннеймановским принципом программного

управления. Согласно этому принципу соседние команды программы

располагаются в ячейках памяти со следующими по порядку адресами и

выполняются преимущественно в той же очередности, в какой они размещены

в памяти ЭВМ. Таким образом, адрес очередной команды может быть получен

путём увеличения адреса ячейки, из которой была считана текущая

команда, на длину выполняемой команды, представленную числом занимаемых

ею ячеек. Реализацию такого режима и призван обеспечивать счетчик

команд — двоичный счетчик, в котором хранится и модифицируется адрес

очередной команды программы. Перед началом вычислений в СК заносится

адрес ячейки основной памяти, где хранится команда, которая должна быть

выполнена первой. В процессе выполнения каждой команды путем увеличения

содержимого СК на длину выполняемой команды в счетчике формируется

адрес следующей подлежащей выполнению команды. В данном случае любая

команда занимает одну ячейку, поэтому содержимое СК увеличивается на

единицу. По завершении текущей команды адрес следующей команды

программы всегда берется из счетчика команд. Для изменения

естественного порядка вычислений (перехода в иную точку программы)

достаточно занести в СК адрес точки перехода.

Регистр команды

Счетчик команд определяет лишь местоположение команды в памяти, но не

содержит информации о том, что это за команда. Чтобы приступить к

выполнению команды, ее необходимо извлечь из памяти и разместить в

регистре команды (РК). Этот этап носит название выборки команды. Только

с момента загрузки команды в РК она становится «видимой» для

процессора. В РК команда хранится в течение всего времени ее

выполнения.

Регистры общего назначения

Регистры общего назначения (РОН), служат для временного хранения

операндов и результатов вычислений. Это самый быстрый, но и минимальный

по емкости тип памяти, который иногда объединяют понятием

сверхоперативное запомина¬ющее устройство — СОЗУ. Как правило,

количество регистров невелико, хотя в архитектурах с сокращенным

набором команд их число может доходить до не¬скольких десятков.

Индексные регистры

Индексные регистры (ИР) служат для формирования адресов операндов при реализации циклических участков программ.

Регистр признака результата

Регистр признака результата (РПР) предназначен для фиксации и хранения

признака, характеризующего результат последней выполненной

арифметической или логической операции. Такие признаки могут

информировать о равенстве результата нулю, о знаке результата, о

возникновении переноса из старшего разряда, переполнении разрядной

сетки и т. д. Содержимое РПР обычно используется устройством управления

для реализации условных переходов по результатам операций АЛУ. Под

каждый из возможных признаков отводится один разряд РПР.

Аккумулятор

Аккумулятор (Акк) — это регистр, на который возлагаются самые

разнообразные функции. Так, в него предварительно загружается один из

операндов, участвующих в арифметической или логической операции. В Акк

может храниться результат предыдущей команды и в него же заносится

результат очередной операции. Через Акк зачастую производятся операции

ввода и вывода.

Строго говоря, аккумулятор в равной мере можно отнести как к АЛУ, так и

к УУ, а в ЭВМ с регистровой архитектурой его можно рассматривать как

один из регистров общего назначения.

Буфер данных

Буфер данных призван компенсировать разницу в быстродействии

запоминающих устройств и устройств, выступающих в роли источников и

потребителей хранимой информации. В буфер данных при чтении заносится

содержимое ячейки ОП, а при записи — помещается информация, подлежащая

сохранению в ячейке ОП.

Буфер адреса

Наличие буфера адреса также позволяет компенсировать различия в быстродействии оперативной памяти и других устройств ЭВМ.

— BTW Electronic Parts

Описание

Описание:

- NTE1784 — это интегральная схема в 16-выводном корпусе типа DIP, предназначенная для использования в качестве горизонтального

- Схема процессора для Ч / Б и цветных телевизионных приемников.

Характеристики:

- Сепаратор горизонтальной синхронизации с шумоподавлением

- Сепаратор вертикальной синхронизации с шумоподавлением

- Осциллятор Horizonyal с ограничителем диапазона частот

- Фазовый компаратор между синхроимпульсами и импульсами генератора (ФАПЧ)

- Фазовый компаратор между импульсами обратного хода и импульсами генератора (ФАПЧ)

- Контурное усиление и переключение с постоянной времени (ВКМ)

- Генератор комбинированного гашения и ключевых импульсов

- Цепи защиты

- Выходные каскады с возможностью высокого тока

Абсолютные максимальные рейтинги:

- (TA = + 25 ° C, если не указано иное)

- Напряжение питания (контакт 1), VS.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 В

- Напряжение цепи, В2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 В

- Напряжение цепи, В4, В11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VS

- Напряжение цепи, В8.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VS к −6V

- Напряжение цепи, В 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . От +6 В до −6 В

- Пиковый ток цепи, I2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1А

- Пиковый ток цепи, I3.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 мА

- Ток цепи, I6, I10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 мА

- Ток цепи, I7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 мА

- Суммарное рассеивание мощности (TA ≤ + 70 ° C), Ptot.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Вт

- Диапазон рабочих температур спая, ТДж. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . От −40 ° до + 150 ° C

- Диапазон температур хранения, Tstg. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . От −40 ° до + 150 ° C

- Максимальное тепловое сопротивление, соединение-окружающая среда, RthJA. . . .. . . . . . . . . . . . . . . . . . . . . . 80 ° C / Вт

Простая схема включает вентилятор при обработке

Аннотация: Показана схема, которая определяет температуру удаленного термодиода на кристалле ЦП, ПЛИС, графического процессора или другой высокопроизводительной ИС. Когда температура термодиода превышает предварительно заданную точку срабатывания, включается охлаждающий вентилятор, тем самым обеспечивая простую функцию управления вентилятором.

Охлаждающие вентиляторы широко используются в ПК, рабочих станциях и других системах, которые могут выделять значительное количество тепла во время нормальной работы.Однако во многих таких системах охлаждение не требуется в 100% случаев. В этих системах предпочтительнее включать вентилятор только при необходимости охлаждения, а не постоянно. Использование вентилятора только при необходимости увеличивает срок его службы и снижает уровень шума системы.Схема, показанная ниже, использует очень простой и недорогой подход к управлению работой вентилятора на основе температуры кристалла микропроцессора, FPGA или другого высокомощного чипа. Целевая ИС должна иметь доступный термочувствительный PN-переход (обычно база и эмиттер PNP-подложки).Схема основана на дистанционном переключателе температуры MAX6513 (IC1). IC1 пропускает ток с точно контролируемыми соотношениями через чувствительный переход на целевой ИС, измеряет прямое напряжение перехода при каждом токе и вычисляет температуру удаленного перехода на основе этой информации. Если измеренная температура превышает установленную на заводе пороговую температуру, выходной контакт MAX6513 (TOVER) становится активным, включая N-канальный полевой МОП-транзистор и подает питание на вентилятор.

Пороговая температура может быть выбрана в соответствии с потребностями целевой ИС.В показанной здесь схеме IC1 имеет порог 55 ° C. Типичные значения для управления вентилятором находятся в диапазоне от примерно 45 ° C до примерно 65 ° C, но могут быть приняты и более высокие значения. После включения вентилятора гистерезис удерживает вентилятор включенным до тех пор, пока температура не упадет на 10 ° C ниже температуры срабатывания. Если предпочтителен гистерезис 5 ° C, подключите контакт HYST к земле. Для достижения наилучших результатов расположите IC1 близко к целевой ИС и держите высокоскоростные цифровые трассы подальше от трасс DXP и DXN, чтобы избежать помех.

Рисунок 1.Этот простой контроллер вентилятора включает вентилятор, когда температура целевой ИС превышает 55 ° C.

Рисунок 2. Вентилятор включается при превышении температуры отключения. Перед выключением вентилятора температура должна упасть ниже температуры отключения за вычетом гистерезиса. Подключив контакт HYST к земле или V CC , можно выбрать гистерезис 5 ° C или 10 ° C.

| ©, Maxim Integrated Products, Inc. |

| ПРИЛОЖЕНИЕ 481: ПРИМЕЧАНИЕ ПО ПРИМЕНЕНИЮ 481, AN481, АН 481, APP481, Appnote481, Appnote 481 |

maxim_web: en / products / сенсоры, maxim_web: en / products / сенсоры и интерфейс сенсоров

maxim_web: en / products / сенсоры, maxim_web: en / products / сенсоры и интерфейс сенсоров